A thesis submitted in partial fulfillment of the requirements for the degree of Master of Science in Electrical Engineering

by

Brett W. Shook University of Arkansas Bachelor of Science in Electrical Engineering

> May 2014 University of Arkansas

| This thesis is approved for recommend   | ation to the Graduate Council. |  |

|-----------------------------------------|--------------------------------|--|

|                                         |                                |  |

|                                         |                                |  |

| Dr. H. Alan Mantooth<br>Thesis Director |                                |  |

| Dr. Simon Ang                           | Dr. Randy Brown                |  |

#### **ABSTRACT**

This thesis presents the design and implementation of a software tool, referred to as PowerSynth, which is used to synthesize multi-chip power module (MCPM) layouts and also aids in the overall design process. MCPMs allow power electronics systems to achieve higher efficiencies and reduced size, weight, and cost through the compact integration of devices into a single package. MCPM design is highly multidisciplinary which involves electrical, thermal, and mechanical performance considerations. Conventionally, the design process may require several iterations and multiple software modeling tools to create high performance MCPMs. The layout of an MCPM consists of a pattern of metal traces and the placement of components on these traces. The design of an MCPM layout and the selection of materials, dimensions, and components used in an MCPM affect its performance. PowerSynth incorporates thermal and electrical models into a single tool and provides a unified system for designing MCPMs and synthesizing layouts for them. A user is guided through the design process with graphical user interfaces and is able to select from a set of solutions which trade-off thermal and electrical performance. Final MCPM designs can be exported to two different commercial modeling tools for further performance verification or for manufacturing artwork generation.

©2014 by Brett Shook All Rights Reserved

### **ACKNOWLEDGEMENTS**

The process of writing this piece of software has taught me an immense amount about a diverse set of topics such as finite element analysis, thermal and electrical modeling, optimization, software development, etc. I would like to thank Dr. Mantooth for setting me on this journey through such a wide range of material and his leadership throughout the project. Dr. Matt Francis has mentored me meeting by meeting every week for several years helping to dispel uncertainty and promote understanding. Dr. Yongfeng Feng also mentored me throughout the beginning of this project and spent many late nights working out problems with me. This work has been made possible by the GRid-connected Advanced Power Electronic Systems (GRAPES) NSF research center. The industry advisory board of this organization has provided me many insights into what is truly needed to improve the engineering of power electronics. Brice McPherson and Jack Bourne at Arkansas Power Electronics International (APEI) provided key information on the design process of MCPMs and many interesting discussions.

Zihao Gong, my initial partner on this project, always kept a positive attitude and spent countless hours working with me to develop the tool. Undergraduates Peter Tucker and Seth Mayfield did a prodigious job helping put together the user interfaces and several extremely useful export functions. Matt Barlow provided great insight into his technical challenges regarding power module design. Dr. Simon Ang, Dr. Shirley Zhang, and Atanu Dutta provided the project with real world module layouts and data which was immensely helpful. Dr. Randy Brown taught me much throughout my degree and guided me through the process. Kathy Kirk has worked tirelessly to help facilitate communication between all parties. I would like to thank everyone mentioned above and anyone else who has helped me through this process.

# TABLE OF CONTENTS

| Chapter 1 Introduction                                           | 1  |

|------------------------------------------------------------------|----|

| 1.1 Background and Motivation                                    | 1  |

| 1.2 MCPM Nomenclature and Spatial Orientation                    | 4  |

| 1.3 Thermal and Electrical Modeling                              | 8  |

| 1.4 Optimization                                                 | 9  |

| 1.5 Symbolic Layout System                                       | 10 |

| 1.6 Software Design and Integration                              | 10 |

| 1.7 Thesis Outline                                               | 12 |

| Chapter 2 Thermal Modeling and Automatic Device Characterization | 13 |

| 2.1 Introduction                                                 | 13 |

| 2.2 Thermal Modeling Algorithm                                   | 13 |

| 2.3 Automatic Thermal Characterization                           | 18 |

| 2.3.1 FEM Tool Background                                        | 18 |

| 2.3.2 FEM Tool Selection                                         | 19 |

| 2.3.3 Meshing with Gmsh                                          | 20 |

| 2.3.4 Finite Element Analysis with Elmer                         | 22 |

| Chapter 3 Electrical Parasitic Modeling and Extraction Algorithm | 25 |

| 3.1 Introduction                                                 | 25 |

| 3.2 Parasitic Resistance and Inductance Modeling                 | 25 |

| 3.3 Parasitic Capacitance Modeling                               | 27 |

| 3.4 Parasitic Extraction Algorithm                               | 28 |

| 3.5 Parasitic Network Measurement                                | 36 |

| 3.6 Parasitic Extraction Results                                 | 38 |

| Chapter 4 Multi-Objective Optimization                           | 44 |

| 4.1 Introduction                                                 | 44 |

| 4.2 Pareto Frontiers and Multi-Objective Optimization            | 45 |

| 4.3 NSGA-II                                                      | 49 |

| Chapter 5 Symbolic Layout                                        | 52 |

| 5.1 Introduction                                                 | 52 |

| 5.2 Symbolic Layouts and Matrix Representation                 | 54  |

|----------------------------------------------------------------|-----|

| 5.3 Layout Design Variable Extraction                          | 58  |

| 5.4 Trace Layout Generation                                    | 64  |

| 5.5 Super Traces                                               |     |

| 5.6 Component Placement                                        | 74  |

| 5.7 Design Variable Correlations and Constraints               | 78  |

| 5.8 Design Rule Checking                                       | 79  |

| Chapter 6 Software Design and Integration                      | 83  |

| 6.1 Introduction                                               | 83  |

| 6.2 Software Data Structures                                   | 83  |

| 6.3 Software Flow                                              | 88  |

| Chapter 7 Graphical User Interfaces                            | 91  |

| 7.1 Introduction                                               | 91  |

| 7.2 Technology Library Editor                                  | 91  |

| 7.3 Project Builder                                            | 94  |

| 7.4 Solution Browser                                           | 100 |

| Chapter 8 Results                                              | 103 |

| 8.1 Design Example (P-Cell N-Cell Half-Bridge Inverter Module) | 103 |

| 8.2 Optimization Objectives                                    | 104 |

| 8.3 Devices and Heat Flow                                      | 105 |

| 8.4 Symbolic Layouts                                           | 105 |

| 8.5 Layout Results                                             | 107 |

| 8.6 Human Design Comparison and Analysis                       | 111 |

| Chapter 9 Conclusions and Future Work                          | 114 |

| 9.1 Summary                                                    | 114 |

| 9.2 Conclusions                                                |     |

| 9.3 Future Work and Recommendations                            |     |

# LIST OF FIGURES

| Fig. 1.1: Catastrophic failure of an MCPM.                                                                     | 2     |

|----------------------------------------------------------------------------------------------------------------|-------|

| Fig. 1.2: Parts of an MCPM.                                                                                    | 5     |

| Fig. 1.3: Bare die vertical MOSFET.                                                                            | 6     |

| Fig. 1.4: Loop Inductance. (a): Main switching loop inductance with current path marked.                       | (b):  |

| Gate loop inductance with current path marked.                                                                 | 7     |

| Fig. 1.5: Overall software flowchart.                                                                          | 11    |

| Fig. 2.1: Cross section of MCPM showing thermal boundary conditions                                            | 14    |

| Fig. 2.2: Lumped element heat transfer network representation of MCPM.                                         | 15    |

| Fig. 2.3: Thermal model rectangular contours. (a): Temperature contours intersecting                           | with  |

| neighboring die. (b): Heat flux contours intersecting with trace.                                              | 16    |

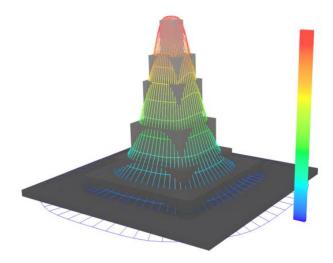

| Fig. 2.4: Temperature distribution overlaid with rectangular contour approximation                             | 17    |

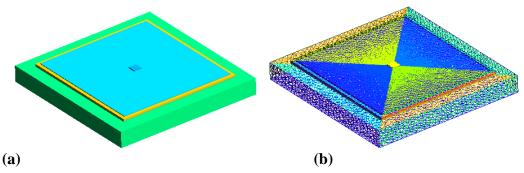

| Fig. 2.5: Module characterization setup with die in center. (a): Surface rendering of module.                  | (b):  |

| Module model with meshing.                                                                                     | 21    |

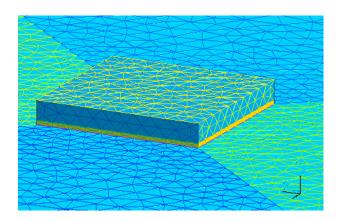

| Fig. 2.6: Close-up of meshed die and die attach layers.                                                        | 21    |

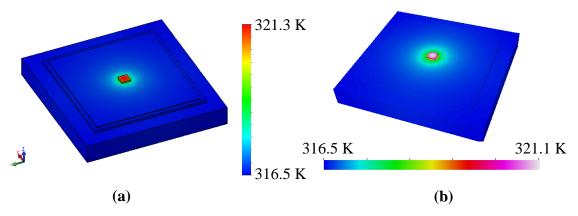

| Fig. 2.7: Steady State Thermal Simulation Results. (a): Result from SolidWorks. (b): Result f                  | rom   |

| Elmer.                                                                                                         | 23    |

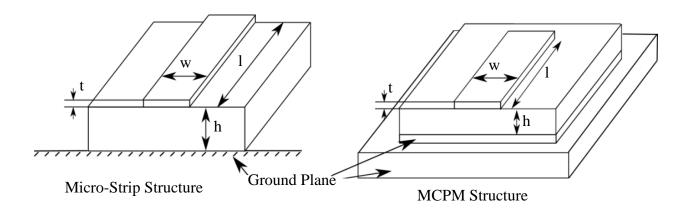

| Fig. 3.1: Comparison of micro-strip transmission line structure and MCPM structure [8]                         | 26    |

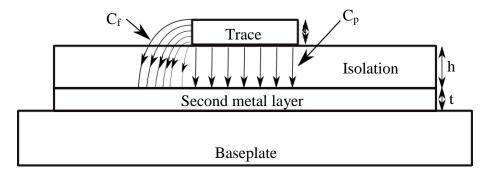

| Fig. 3.2: Parallel plate and fringing field lines which make up parasitic capacitance [8]                      | 27    |

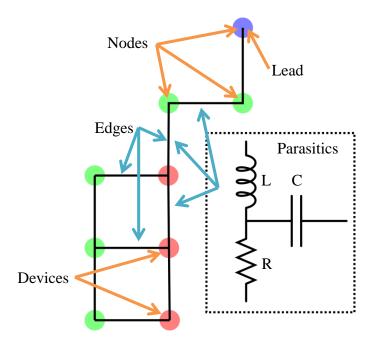

| Fig. 3.3: Graph based representation of parasitic network.                                                     | 30    |

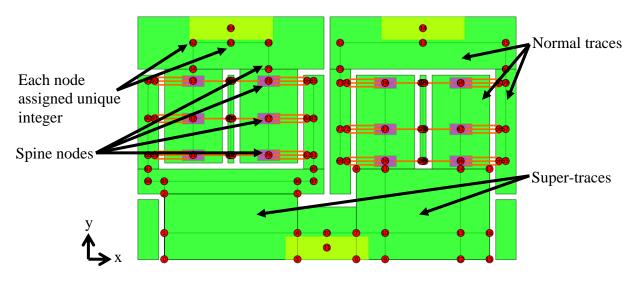

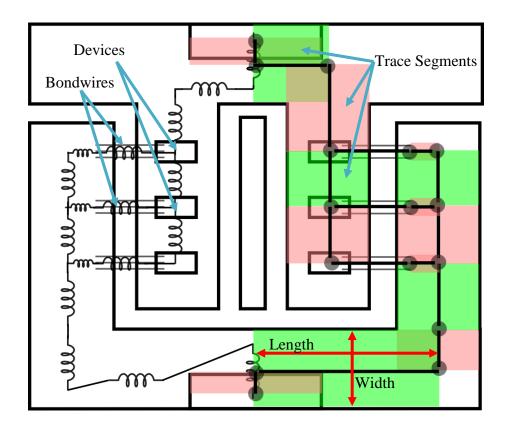

| Fig. 3.4: Module layout with overlaid parasitic graph.                                                         | 31    |

| Fig. 3.5: Parasitic extraction lumped element network and trace segmentation                                   | 34    |

| Fig. 3.6: Super-trace segmentation with segment widths marked with yellow lines. (a): Ver                      | tical |

| segments. (b): Horizontal segments.                                                                            | 35    |

| Fig. 3.7: Graph and Laplacian matrix with all edges weighted to 1.0 (1.0 $\Omega$ ).                           | 36    |

| Fig. 3.8: Parasitic extraction test layouts. (a): Simple layout. (b): Complex layout 1. (c): Complex layout 1. | plex  |

| layout 2                                                                                                       | 40    |

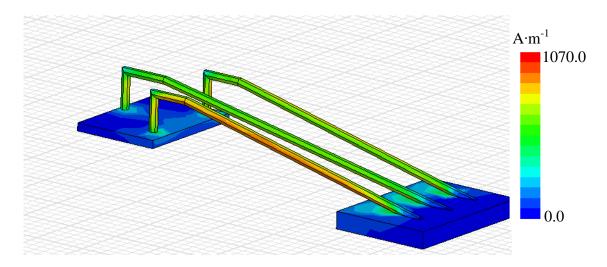

| Fig. 3.9: Bondwire experiment showing increased current density in outer wires                                 | 43    |

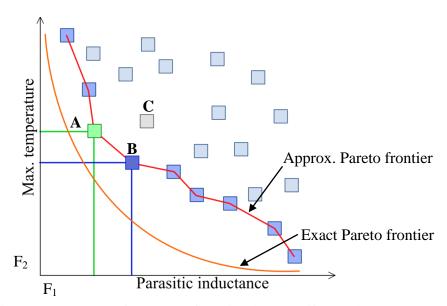

| Fig. 4.1: Example of a Pareto frontier (trade-off curve).                                                      | 47    |

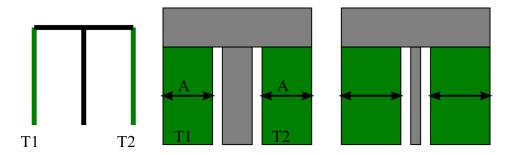

| Fig. 5.1: Symbolic layout with two different geometric layouts. (a): Symbolic layout. (b)         | b): |

|---------------------------------------------------------------------------------------------------|-----|

| Geometric layout 1. (c): Geometric layout 2.                                                      | 53  |

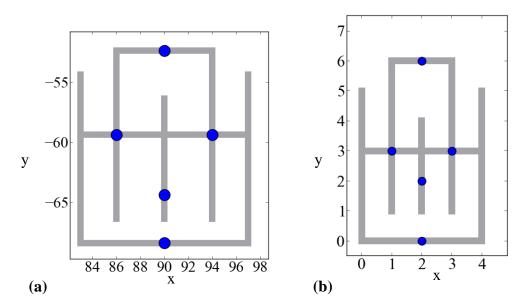

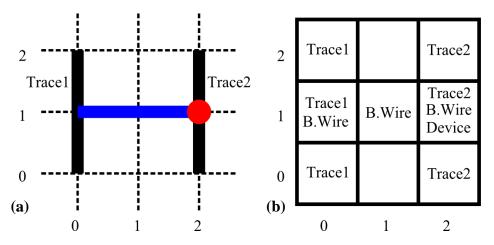

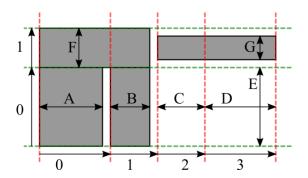

| Fig. 5.2: Symbolic layout normalization. (a): Un-normalized layout. (b): Normalized layout        | 55  |

| Fig. 5.3: Normalized layout to matrix representation. (a): Normalized layout. (b): Matrix da      | ata |

| structure with pointers to layout objects.                                                        | 57  |

| Fig. 5.4: Normalized symbolic layout and matrix with only traces. (a): Normalized trace specific  | fic |

| layout. (b): Trace specific matrix data structure.                                                | 57  |

| Fig. 5.5: Two trace layouts derived from the same symbolic layout. (a): Trace layout 1. (b)       | b): |

| Trace layout 2.                                                                                   | 59  |

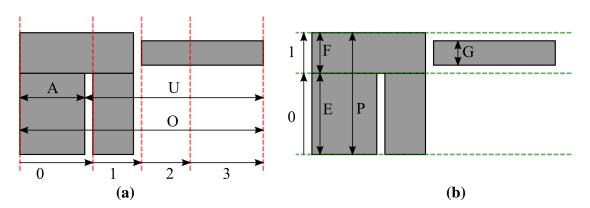

| Fig. 5.6: A slightly more complicated trace specific layout. (a): Trace specific layout. (b): Tra | ice |

| specific matrix                                                                                   | 61  |

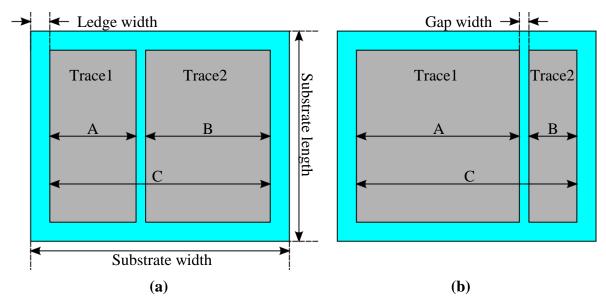

| Fig. 5.7: Geometric trace layout example with design variables.                                   | 64  |

| Fig. 5.8: Finding removed design variable widths. (a): Horizontal case where A is found. (b)      | b): |

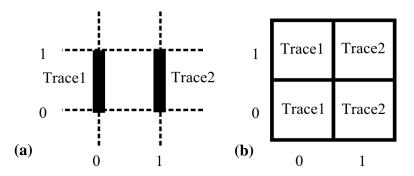

| Vertical case where E is found                                                                    | 67  |

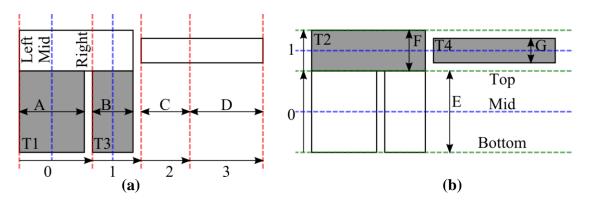

| Fig. 5.9: Parallel trace rectangle generation. (a): Horizontal process. (b): Vertical process     | 70  |

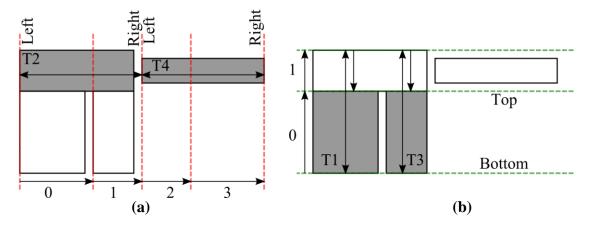

| Fig. 5.10: Orthogonal trace rectangle generation process. (a): Horizontal process. (b): Vertical  | cal |

| process                                                                                           | 73  |

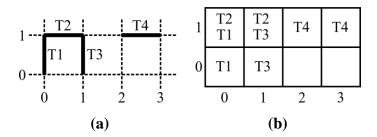

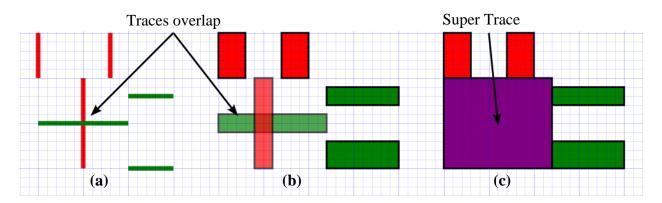

| Fig. 5.11: Super trace formation. (a): Symbolic layout. (b): Overlapping rectangles after tra     | ice |

| rectangle generation. (c): Super trace replacement.                                               | 74  |

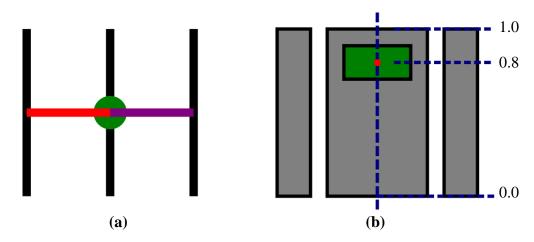

| Fig. 5.12: Device placement. (a): Symbolic layout. (b): Geometric layout with device placed       | at  |

| 80% length of trace.                                                                              | 75  |

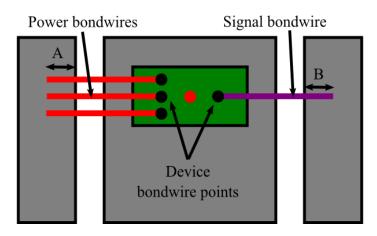

| Fig. 5.13: Bondwire placement.                                                                    | 76  |

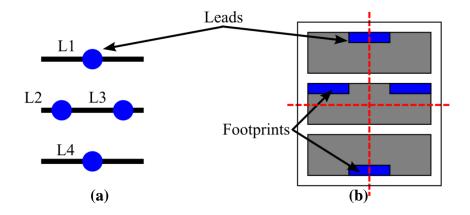

| Fig. 5.14: Lead placement example. (a): Symbolic layout. (b): Geometric layout                    | 77  |

| Fig. 5.15: Design variable correlation between traces T1 and T2.                                  | 78  |

| Fig. 5.16: Process design rules for MCPM.                                                         | 80  |

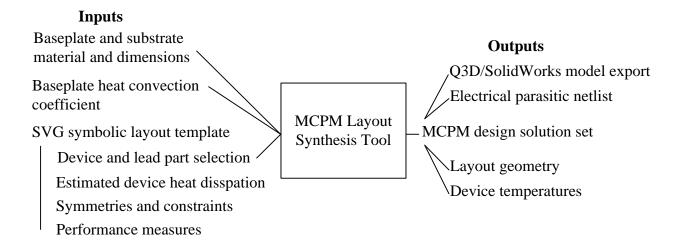

| Fig. 6.1: Overall input and output of layout tool.                                                | 89  |

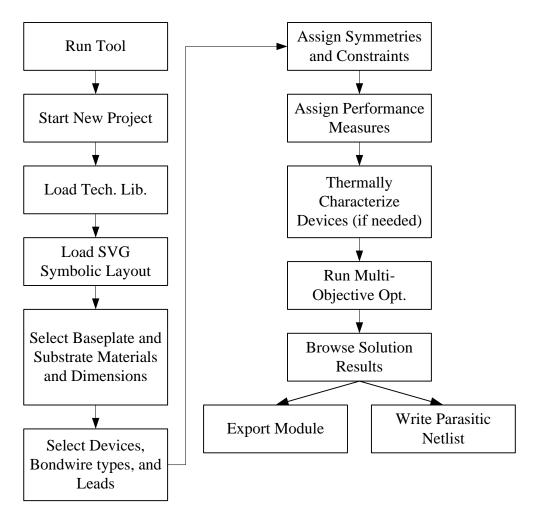

| Fig. 6.2: Software flowchart.                                                                     | 90  |

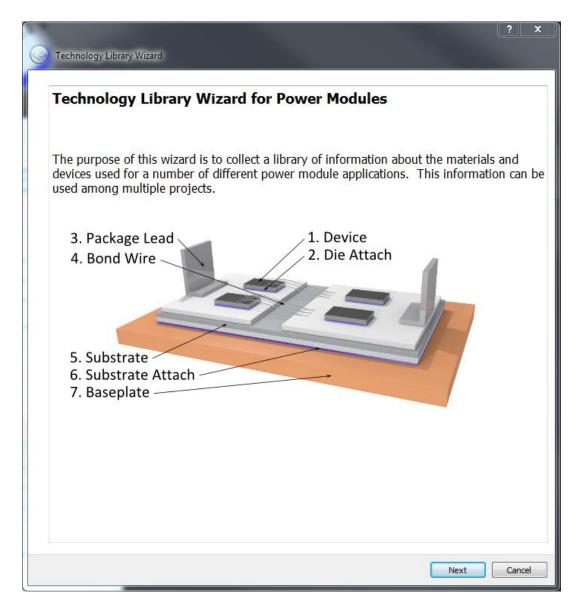

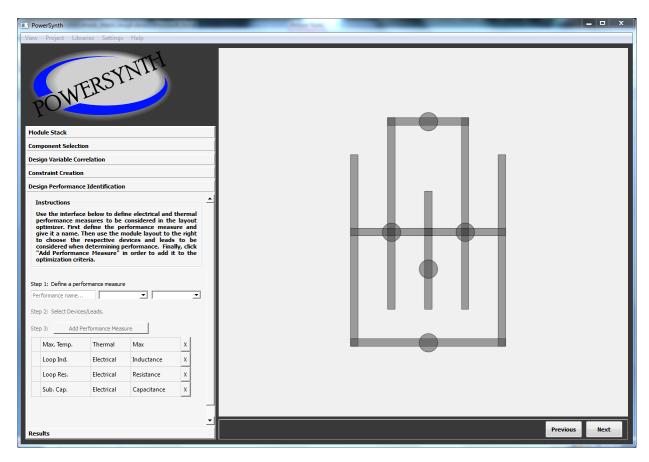

| Fig. 7.1: Start-up screen for technology library editor/wizard (the above software screenshot     | is  |

| intended only to give the reader a sample view of the software discussed)                         | 92  |

|                                                                                                   |     |

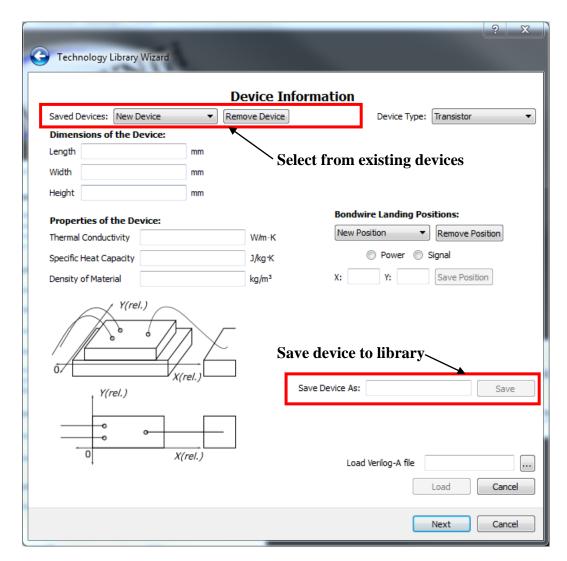

| Fig. | 7.2: | Device page for technology library editor (the above software screenshot is intended     |

|------|------|------------------------------------------------------------------------------------------|

|      |      | only to give the reader a sample view of the software discussed)                         |

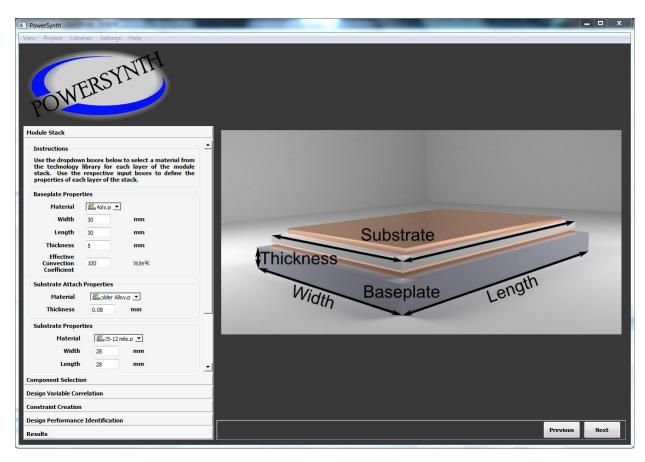

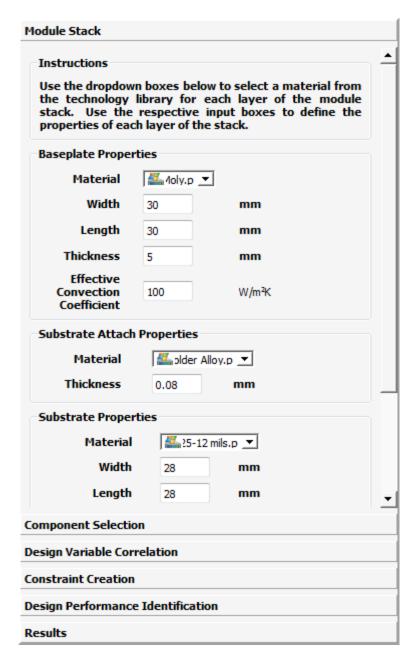

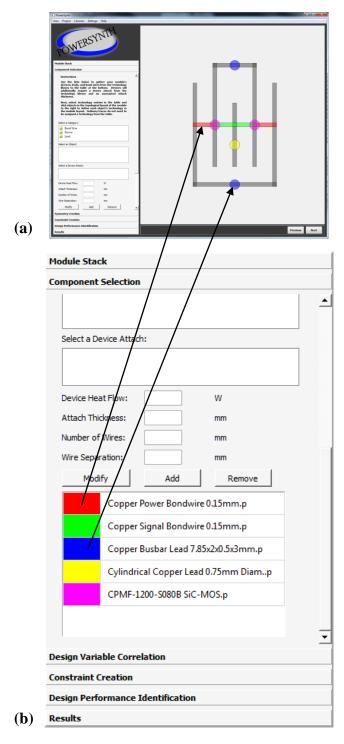

| Fig. | 7.3: | Project Builder interface with the Module Stack page selected (the above software        |

|      |      | screenshot is intended only to give the reader a sample view of the software discussed). |

|      |      | 95                                                                                       |

| Fig. | 7.4: | Navigation and data entry component (the above software screenshot is intended only to   |

|      |      | give the reader a sample view of the software discussed)                                 |

| Fig. | 7.5: | Screen capture of Component Selection page (the above software screenshot is intended    |

|      |      | only to give the reader a sample view of the software discussed). (a): Overall page with |

|      |      | interactive symbolic layout. (b): Close-up of list of selected components                |

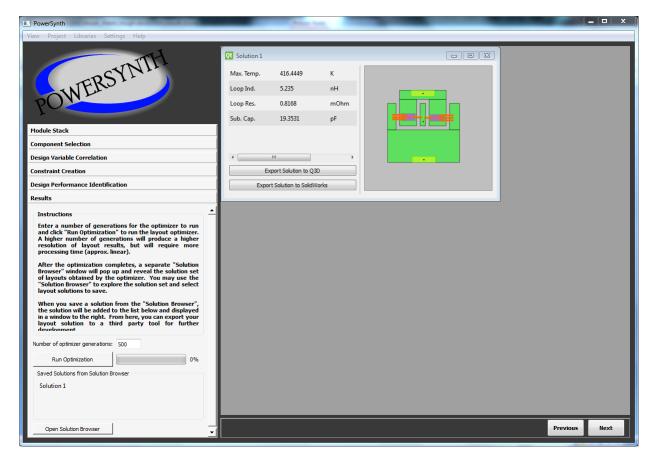

| Fig. | 7.6: | Results page (the above software screenshot is intended only to give the reader a sample |

|      |      | view of the software discussed).                                                         |

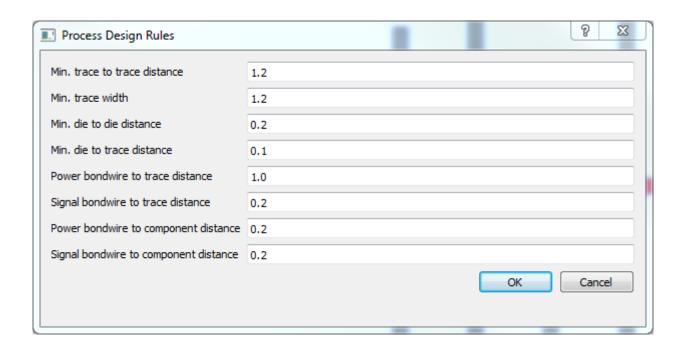

| Fig. | 7.7: | Screen capture of Process Design Rules Editor dialog (the above software screenshot is   |

|      |      | intended only to give the reader a sample view of the software discussed) 100            |

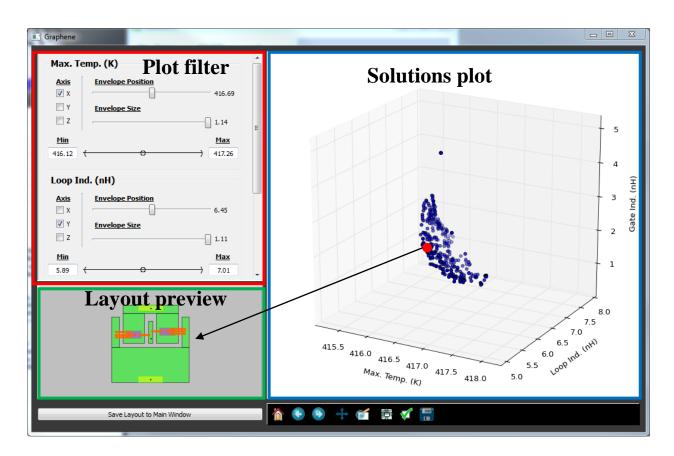

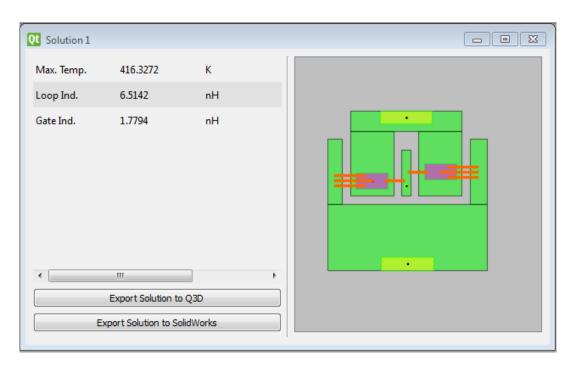

| Fig. | 7.8: | Solution Browser window (the above software screenshot is intended only to give the      |

|      |      | reader a sample view of the software discussed)                                          |

| Fig. | 7.9: | Saved solution sub-window within the Project Builder (the above software screenshot is   |

|      |      | intended only to give the reader a sample view of the software discussed) 102            |

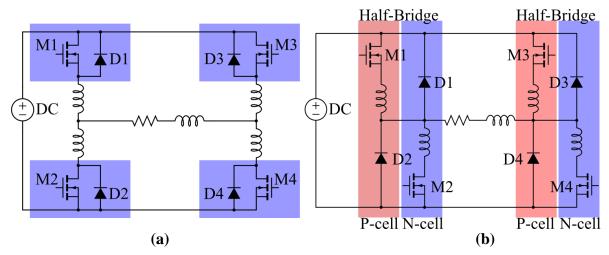

| Fig. | 8.1: | Schematic of full-bridge inverter with parasitic inductance. (a): Diodes internal to     |

|      |      | MOSFETS. (b): P-cell N-cell paring                                                       |

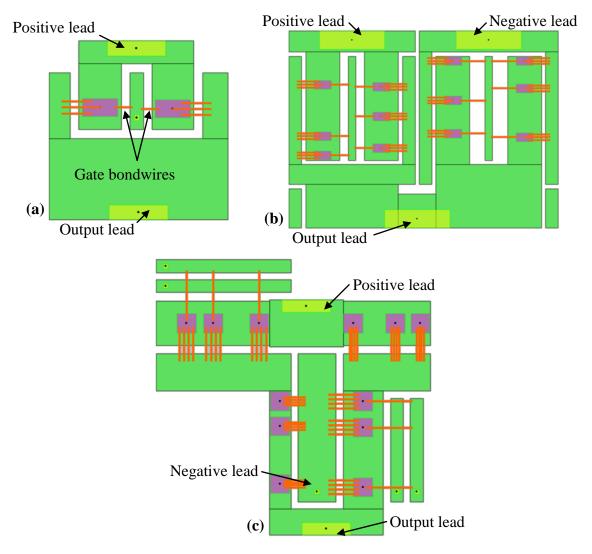

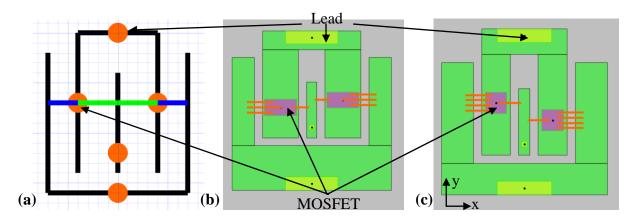

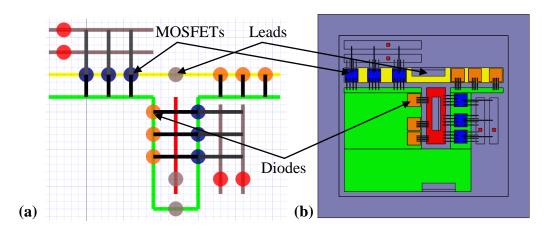

| Fig. | 8.2: | Symbolic layout A. (a): Stick figure diagram. (b): A geometric solution                  |

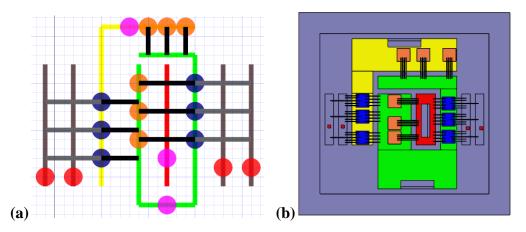

| Fig. | 8.3: | Symbolic layout B. (a): Stick figure diagram. (b): A geometric solution                  |

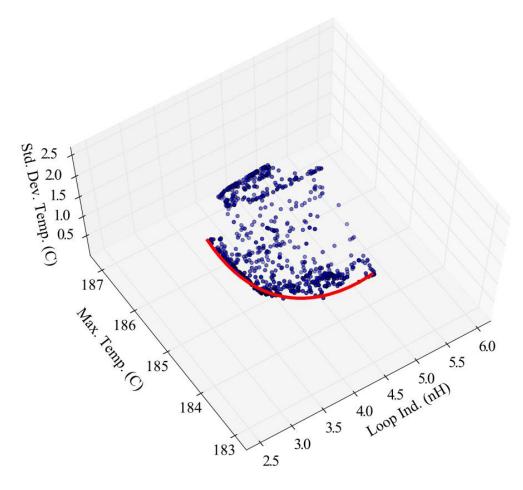

| Fig. | 8.4: | Pareto front of symbolic layout A                                                        |

| Fig. | 8.5: | Pareto front of symbolic layout B                                                        |

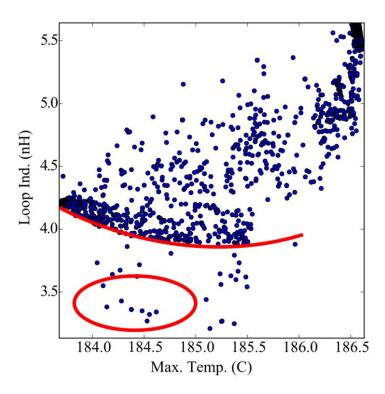

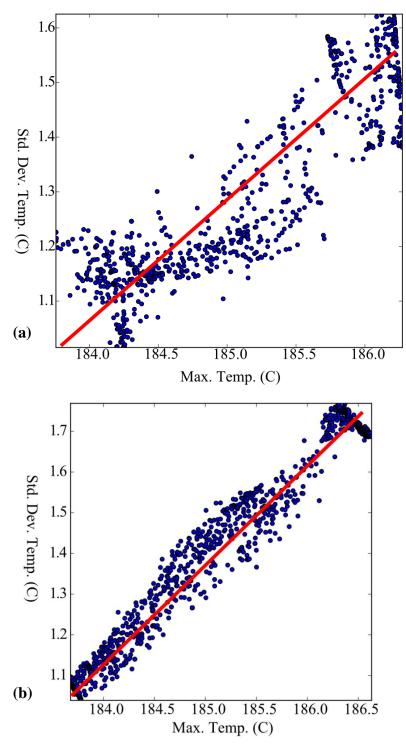

| Fig. | 8.6: | Linear relation between max. and std. dev. of device temperatures. (a): Symbolic layout  |

|      |      | A. (b): Symbolic layout B                                                                |

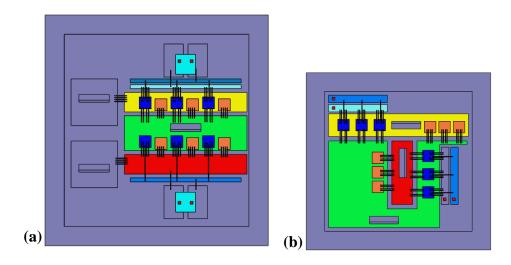

| Fig. | 8.7: | Human Designed Layouts. (a): Conventional Layout. (b): PN Layout                         |

# LIST OF APPENDIX FIGURES

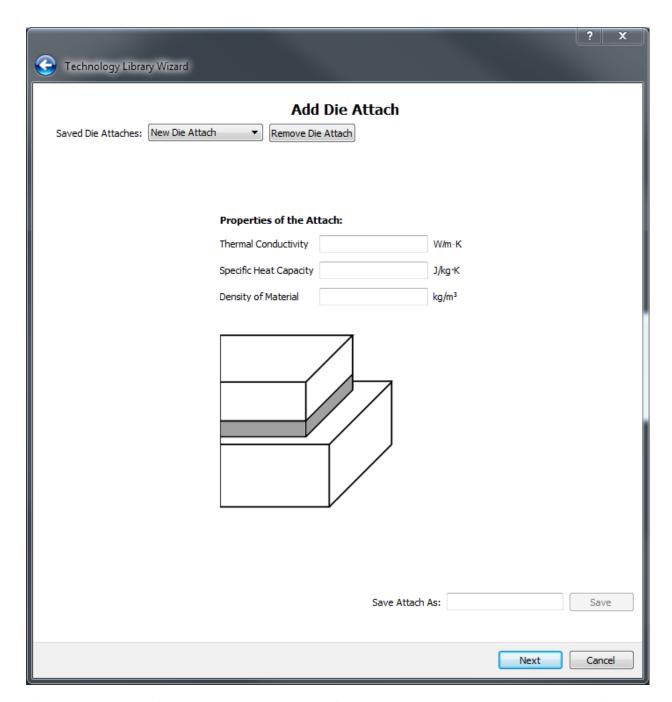

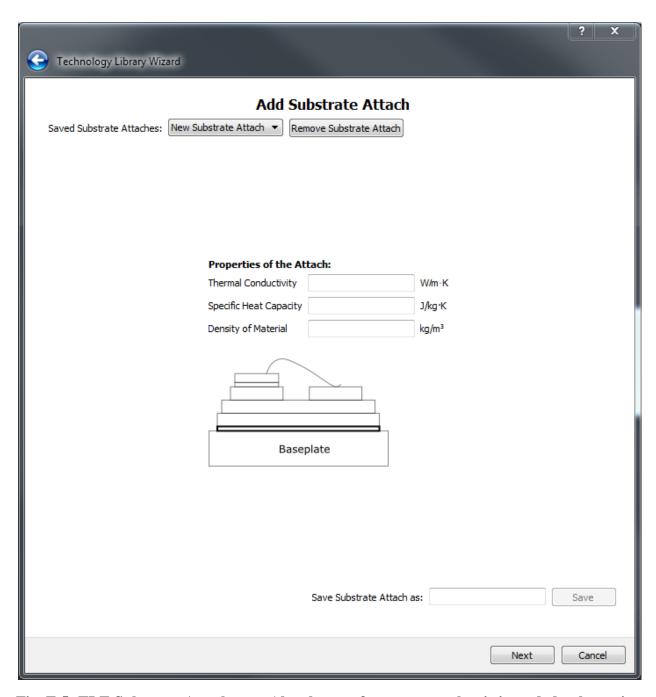

| Fig. E.1: TLE Die Attach page (the above software screenshot is intended only to give the reader  |

|---------------------------------------------------------------------------------------------------|

| a sample view of the software discussed)                                                          |

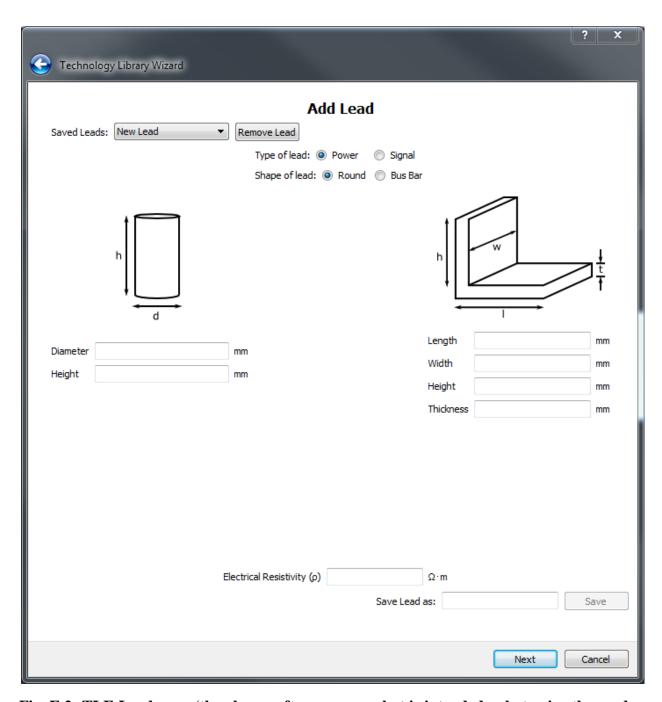

| Fig. E.2: TLE Lead page (the above software screenshot is intended only to give the reader a      |

| sample view of the software discussed)                                                            |

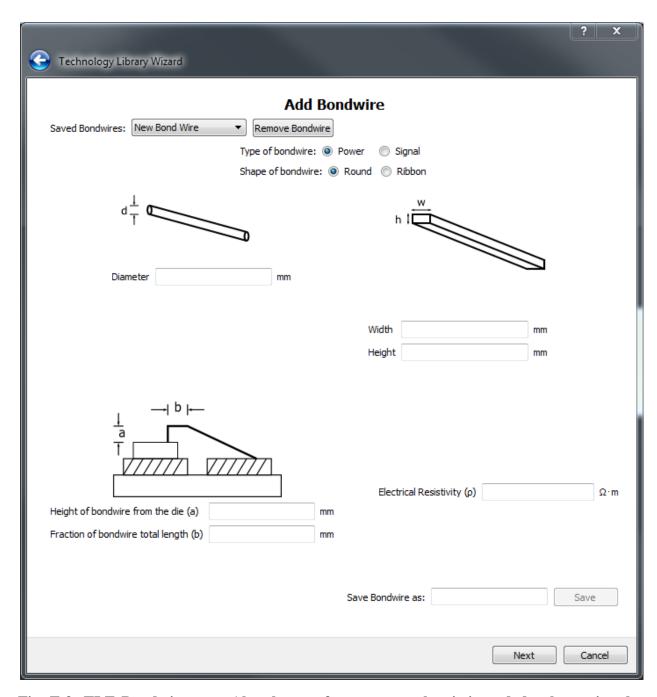

| Fig. E.3: TLE Bondwire page (the above software screenshot is intended only to give the reader    |

| a sample view of the software discussed)                                                          |

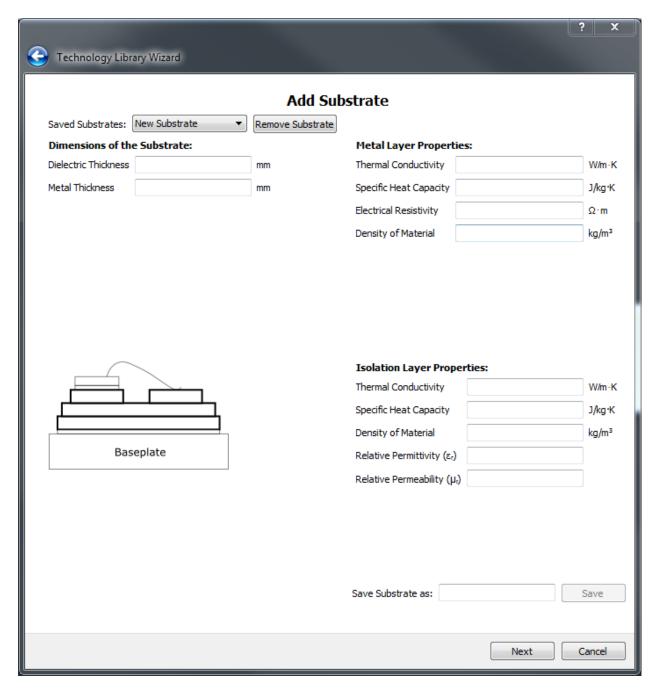

| Fig. E.4: TLE Substrate page (the above software screenshot is intended only to give the reader a |

| sample view of the software discussed)                                                            |

| Fig. E.5: TLE Substrate Attach page (the above software screenshot is intended only to give the   |

| reader a sample view of the software discussed)                                                   |

| Fig. E.6: TLE Baseplate page (the above software screenshot is intended only to give the reader a |

| sample view of the software discussed)                                                            |

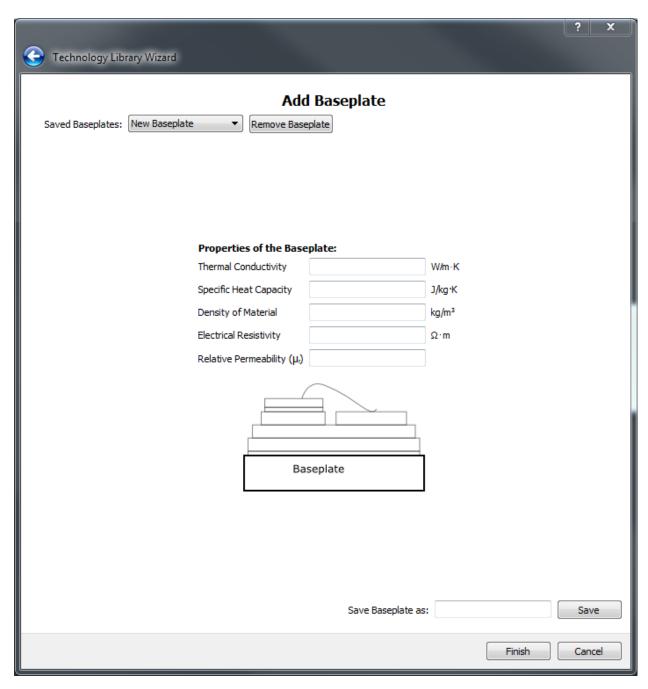

| Fig. F.1: Design Variable Correlation page (the above software screenshot is intended only to     |

| give the reader a sample view of the software discussed)                                          |

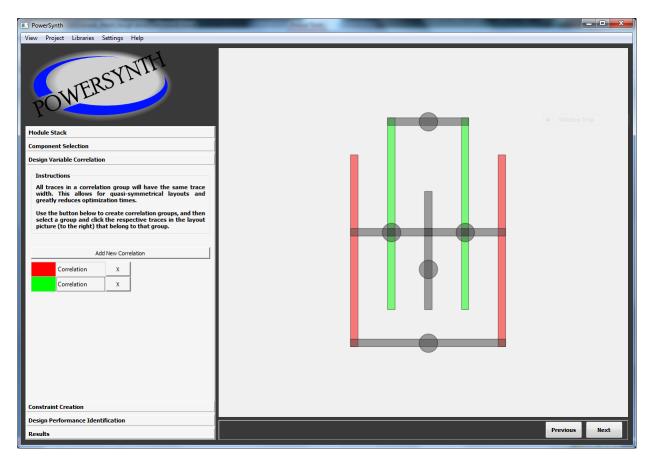

| Fig. F.2: Constraint Creation page (the above software screenshot is intended only to give the    |

| reader a sample view of the software discussed)                                                   |

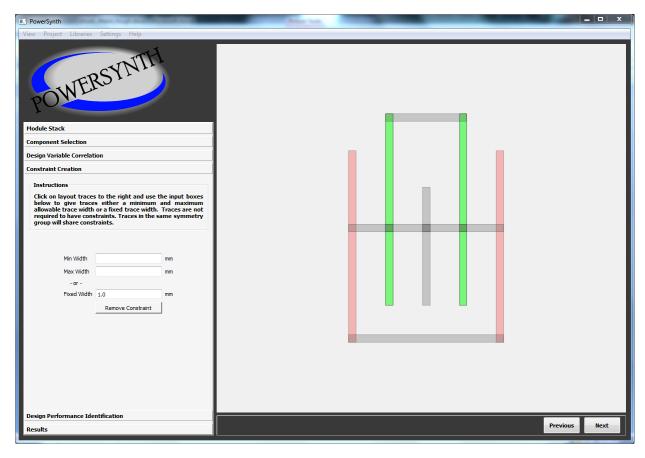

| Fig. F.3: Design Performance Identification page (the above software screenshot is intended only  |

| to give the reader a sample view of the software discussed)                                       |

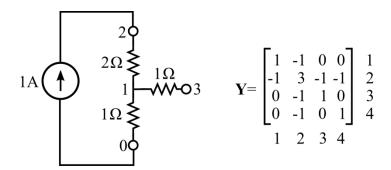

| Fig. G.1: Simple circuit and its Laplacian matrix.                                                |

| Fig. G.2: Moore-Penrose pseudoinverse results                                                     |

| Fig. G.3: Current vector and voltage output vector                                                |

# LIST OF TABLES

| Table 2.1: SolidWorks vs. Elmer FEA results.                          | 24  |

|-----------------------------------------------------------------------|-----|

| Table 3.1: Parasitic extraction comparison between fast model and Q3D | 41  |

| Table 5.1: Process design rules and symbols used in Fig. 5.16.        | 80  |

| Table 6.1: MCPM parts and levels of abstraction                       | 84  |

| Table 8.1: Layout Performance Results.                                | 112 |

## **Chapter 1** Introduction

### 1.1 Background and Motivation

Power electronics modules are used to control the flow of electrical energy to or from electrical systems such as batteries, electric motors, the grid, renewable energy sources, etc. They are responsible for large increases of efficiency in manufacturing and many other areas involving energy transfer. An ideal power module is low cost, small in size, highly efficient, and highly reliable.

These goals are primarily achieved by increasing the switching frequency at which a module operates. The switching frequency determines how fast the semiconductor devices inside the power module are modulated to control the flow of power. At higher switching frequencies the passives such as capacitors, inductors, and high frequency transformers connected to the module can generally be reduced in size. This reduces the cost of the overall system and increases efficiency [1]. However, as the switching frequency is increased past some threshold, depending on the module parasitics and semiconductor devices, the switching losses eventually overcome the efficiency gains.

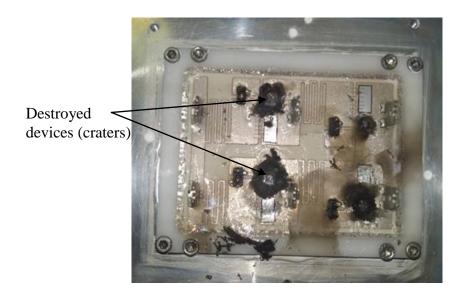

In order to increase the switching frequency of power modules, layout parasitics need to be reduced. A power module layout is the pattern of metal traces and placement of components on the traces. Parasitic inductances in the layout of a module can cause over-voltages across semiconductor devices and EMI issues which can cause reduced operating lifetime or even catastrophic failure of devices, see Fig. 1.1.

Fig. 1.1: Catastrophic failure of an MCPM.

Multi-chip power modules (MCPMs), which are the focus of this thesis, help reduce layout parasitics by integrating multiple bare die power devices and control circuitry into a single package [2]. Integration helps reduce the conductor path lengths between devices, thus reducing parasitic inductance. As devices are integrated into smaller packages, thermal design considerations become important.

Semiconductor devices operating at high frequency may generate up to several watts of waste heat which flows into the surrounding environment. Reducing the size of an MCPM increases heat flux density and device temperature which reduces device operating lifetime and reliability [3]. The heat transfer capability of a module is increased when its volume is increased, because of increased surface area. Spacing devices further from one another also decreases device temperature. The objective of reducing device temperatures is in conflict with the objective of reducing layout parasitics. As a module is decreased in size to decrease parasitics,

the device temperatures increase. Finding the correct trade-off between these two characteristics depends on the application of an MCPM, its intended environment, materials, and components.

The current design process of MCPMs is primarily done manually, although some experimental software tools have been developed to help automate the design problem. An automatic layout design tool for power modules which focuses on minimizing loop inductance and footprint area is presented in [4]. This tool does not consider the temperature of the devices in the module and only considers a single layout parasitic measure (loop inductance). The tool is only able to produce half-bridge topologies. It would be useful for an MCPM layout synthesis and design tool to consider both electrical and thermal performance criteria and other circuit topologies.

A second tool, a predecessor to the tool described in this thesis, models both layout inductance, resistance, and device temperatures [5]. This tool, referred to as PowerCAD, does not consider the trade-off between electrical parasitics and temperature, but treats the maximum temperature in the module as a constraint. A user may need to manually change the thermal constraint multiple times in order to find the correct trade-off between the desired thermal and electrical performance. PowerCAD also only provides support for half-bridge power modules which are configured in a specific ring shaped layout. The conclusions gained from building PowerCAD provided some key insights for building the current iteration of the tool described in this thesis.

The tool presented in thesis, PowerSynth, allows a user to consider the trade-off between thermal and electrical performance and also provides a flexible framework for synthesizing not only half-bridge MCPMs but any circuit topology. The tool is able to generate a set of optimal trade-off MCPM designs considering any number of thermal or electrical performance criteria. PowerSynth includes graphical user interfaces which aid in the problem definition process and browsing of a solution set. A design is selected from this set and is easily exported to two different commercial modeling tools that subsequently allow generation of manufacturing artwork for fabrication.

## **1.2 MCPM Nomenclature and Spatial Orientation**

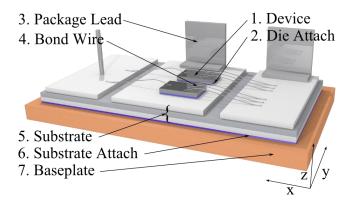

An MCPM is composed of several different layers and components as shown in Fig. 1.2. The bottommost layer is a baseplate or heat spreader which helps dissipate waste heat from the semiconductor devices at the top of the module. A substrate layer resides on top of the baseplate and is formed out of a dielectric isolation layer which is surrounded by two metal layers. It is bonded to the baseplate by the substrate attach layer which is commonly composed of a solder type material. The dielectric layer of the substrate is usually composed of a ceramic material with high thermal conductivity. The two metal layers are usually composed of either copper or aluminum. The substrate may be referred to as direct bond aluminum (DBA) or direct bond copper (DBC), because the metal layers are directly bonded to the ceramic layer without a separate attachment compound. The metal layers are relatively thick compared to lower power circuit boards which allow them to tolerate high voltages and high currents. The top metal layer is etched to form a pattern of interconnection for the desired layout topology [2].

Fig. 1.2: Parts of an MCPM.

The power semiconductor devices used in MCPMs are usually un-packaged or bare die. The devices are connected to the metal traces by bondwires and by bonding the bottom surface of the die to a trace. The die attach or material that bonds the die to the metal surface is commonly a solder material. Package leads are bonded to the metal trace layer and provide either high power connections to the module or low power signal connections to the control electronics which are commonly integrated at the top. The control electronics may also be integrated onto a separate control substrate which is bonded to the power substrate, but this type of configuration is not targeted in this thesis [2].

The z direction is referred to as the vertical direction throughout the thesis. The thickness dimension runs in the vertical direction while width and length dimensions run in either the x or y directions depending on context.

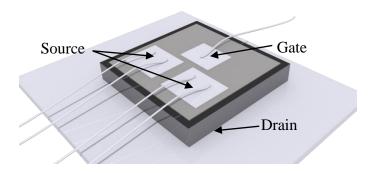

A close-up image of a bare die metal oxide semiconductor field effect transistor (MOSFET) device commonly used in MCPMs is shown in Fig. 1.3. The device is a vertical MOSFET rather than a horizontal or planar MOSFET used in lower power circuitry. Current

flows through a vertical MOSFET from the bottom (drain) to the top (source). The drain is connected to the metal traces with a conductive die attach. Bondwires connect the source and gate pads at the top of the device. Insulated gate bipolar transistors (IGBTs) follow a similar connection pattern, but the terms base, emitter, and collector are used instead of gate, source, and drain for the input ports. IGBT type devices are not included in the tool described in this thesis, but integration for them would be relatively straight forward.

Fig. 1.3: Bare die vertical MOSFET.

Fast switching Schottky diodes are commonly found in MCPM layouts as bare die. The diode die are bonded to the substrate in the same way as MOSFET die. The bottom of a diode die is the cathode and the top pad is the anode. The anode pad on the top of a diode die is wirebonded in the same way as the source or gate connections for a MOSFET die.

The MOSFETs used in MCPMs are usually composed of either silicon (Si) or silicon-carbide (SiC). SiC MOSFETs are becoming more commonly used in MCPMs and other power electronics applications due to their relatively higher thermal conductivity, higher temperature operation, wider band gap, and fast switching rate as compared to Si based MOSFETs. SiC Schottky diodes have already become commonplace in power electronics designs.

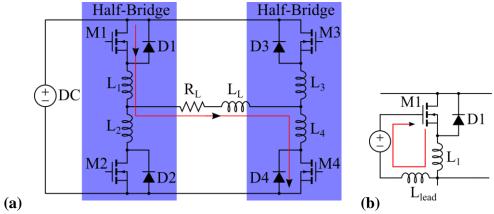

Another term used frequently in reference to MCPMs and power electronics in general is loop inductance. The loop inductance is the amount of parasitic stray inductance in a path or loop in which the current is forced to stop flowing periodically. For example, two half-bridge MCPMs may be connected on either side of a load which is being supplied with an alternating current, see Fig. 1.4(a). The transistors M1 and M4 are turned on in unison to produce a current flowing from left to right through the load. Eventually, this current will be stopped and reversed or commutated by turning off M1 and M4 and turning on M2 and M3. While M1 and M4 are turning off, the current will begin to decrease and voltage will begin rise on the parasitic inductances represented by L<sub>1</sub> and L<sub>4</sub>. If these parasitic inductances are large and the turn-off time is short, a large voltage will form across each inductance which can stress devices and/or decrease switching efficiency [6].

Fig. 1.4: Loop Inductance. (a): Main switching loop inductance with current path marked. (b): Gate loop inductance with current path marked.

The main switching loop inductance for a half-bridge module may be defined as the sum of all of the parasitic stray inductances from the positive to negative terminals such as  $L_1 + L_2$  in the half-bridge on the right in Fig. 1.4(a). Gate loop inductance is also a frequently used term. As transistors are turned on and off during switching, a current appears in the path formed between

the gate and the source of the transistor as shown in Fig. 1.4(b). Minimizing this parasitic inductance may also help reduce ringing effects during switching states of the power transistor [6].

## 1.3 Thermal and Electrical Modeling

Thermal and electrical models are needed in order to evaluate the performance of MCPM designs. Finite element method (FEM) based thermal and electrical models are accurate but computationally expensive and time consuming to evaluate. FEM models are useful for the verification of a final design. PowerSynth uses an optimization algorithm to find many optimal MCPM designs and evaluates thousands of candidate designs in the process. FEM models are generally too slow for this optimization process. Fast thermal and electrical models are needed to perform the optimization process within a reasonable time frame e.g. 5 to 10 minutes.

The fast thermal modeling technique developed specifically for this tool is presented in detail in [7], [8]. The thermal model requires a characterization step to be carried out on each type of semiconductor device in the system. This characterization step provides steady state temperature and heat flux distributions for a device dissipating a constant heat flow. If multiple instances of a device exist in an MCPM, these distributions are placed in superposition. As the device instances are moved around during the optimization process, the device temperatures may be quickly recalculated through superposition. This characterization step has been automated and is presented in this thesis, thus removing any manual FEM modeling by a user.

The electrical parasitic modeling and extraction system is presented in [8], [9]. These works provide information about the physical closed-form equations used to model the parasitic

inductance, resistance, and capacitance of traces in an MCPM layout. These works only describe a parasitic extraction system for a fixed layout configuration and not a full parasitic extraction implementation. A more general parasitic extraction method is presented and tested in this thesis.

## 1.4 Optimization

An optimization process seeks to minimize or maximize a characteristic of a system by varying a set of parameters or variables which define the design of a system. In the case of MCPMs, there are multiple characteristics which are desired to be minimized e.g. maximum module temperature and loop inductance. The objective is to minimize both of these characteristics, but both cannot be minimized simultaneously. As the MCPM design parameters are changed to decrease the maximum module temperature, the loop inductance will increase. A trade-off exists between these two objectives. A multi-objective optimization process seeks to find a set of solutions which provide the best trade-off between all of the objectives. A designer is able to select a solution which best suits the needs of a particular engineering problem. For example, a designer may desire lower temperature operation for improved reliability, but a higher loop inductance which reduces electrical performance.

PowerSynth allows for definition of any number of objectives and is not limited to two. A designer may be interested in minimizing gate loop inductance or minimizing the temperature differences between devices in a layout in addition to reducing maximum temperature and main switching loop inductance.

### 1.5 Symbolic Layout System

A symbolic layout system is developed to provide a framework for defining MCPM layouts without specifying the scale and dimensions of trace or the positions of components. This abstraction allows a layout configuration to be used for multiple projects which have different devices, leads, bondwires, and geometric scales. A vector or list of design variables are extracted from a symbolic layout and passed to the optimizer. The optimizer varies these design variables in order to find optimal layout solutions. The symbolic layout system also forms the groundwork for a fully automated layout synthesis system which would generate layouts from circuit netlists. This goal has not yet been achieved in PowerSynth, but some steps have been taken towards it. An algorithm has been developed to produce symbolic layouts for half-bridge topologies, but this work is still in an experimental phase.

### 1.6 Software Design and Integration

The thermal and electrical models, multi-objective optimizer, and symbolic layout system are integrated together into a single tool using a set of data structures and graphic user interfaces (GUIs). The overall goal of the software is to reduce the amount of time and effort required to design an MCPM and layout. A non-expert in MCPM design should be able to use PowerSynth to design and export an MCPM. The software should also allow for faster design iteration time if multiple design iterations are needed.

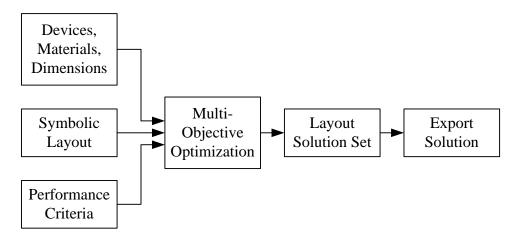

A simplified software flowchart for PowerSynth is shown in Fig. 1.5. A user selects the materials, dimensions, and properties of the baseplate and substrate for an MCPM design. The baseplate and substrate materials are chosen from a technology library which holds material

property information and other data for use on an inter-project basis. A symbolic layout is loaded into the tool and specific device, lead, and bondwire types are chosen from the technology library to represent certain symbolic elements in the layout. Next, a user chooses a set of performance criteria which are critical to the design of the module such as maximum device temperature, loop inductance, etc. Pre-loaded projects may be saved for users with less experience in the design process.

Fig. 1.5: Overall software flowchart.

PowerSynth is composed of three main user interfaces. The first is the Technology Library Editor (TLE) which provides an interface for editing the technology library. The second is the Project Builder. It is used to create MCPM design projects and input the information prior to executing the multi-objective optimization process. The third is the Solution Browser which contains an interactive plot used to select solutions derived from the optimization process. The solutions are plotted against the chosen performance criteria and may be filtered based on desired ranges of criteria e.g. temperature, loop inductance, etc.

#### 1.7 Thesis Outline

Chapters 2 through 5 of this thesis describe the main independent components which form the basis of PowerSynth. Chapter 2 summarizes the thermal modeling approach and presents the automatic device characterization process. Chapter 3 summarizes the electrical parasitic models and elaborates the parasitic extraction and measurement system. An introduction to multi-objective optimization and the specific algorithm used in PowerSynth is given in Chapter 4. All aspects of the symbolic layout system from the loading process of symbolic layouts to the generation of trace geometry and component placement is described in Chapter 5. Chapter 5 also discusses the process design rules and design rule checking for MCPMs.

Chapters 6 and 7 present the integration of these main components into a single software tool. Chapter 6 describes the organization of PowerSynth in terms of data structures and the data flow of the tool from input to output. The graphical user interfaces which guide a user through technology library editing, project setup, and solution selection are discussed in Chapter 7.

The design of a half-bridge module using the P-Cell N-Cell layout technique with PowerSynth is presented in Chapter 8. Human designs are compared with design results using PowerSynth. The thesis is concluded in Chapter 9 with a summary of the work, conclusions gained from the project, and recommendations for future work.

## **Chapter 2** Thermal Modeling and Automatic Device Characterization

#### 2.1 Introduction

The thermal modeling approach developed for the power module layout synthesis tool is presented in [7] and [8] in further detail, but it is covered briefly in the next section before the automatic characterization process is explained in detail. This fast thermal model is sufficiently accurate to be effective in an optimization framework and yet typically executes four orders of magnitude faster than FEM models. The fast thermal modeling method requires an initial characterization step where a finite element method (FEM) based simulation is conducted in order to find temperature and heat flux distributions which emanate from a die given the materials and dimensions for the baseplate and substrate of a module. These distributions allow for prediction of die temperatures in a module with modifications to trace layout, die positioning, and die quantities. The automatic characterization process of a fast, low order thermal model presented in this chapter describes how an FEM model of a module is constructed, meshed, and solved automatically to gain temperature and heat flux distribution information without any manual labor from the user. This reduces errors in the characterization process and greatly reduces time and effort of introducing new devices and new module configurations into the tool.

#### 2.2 Thermal Modeling Algorithm

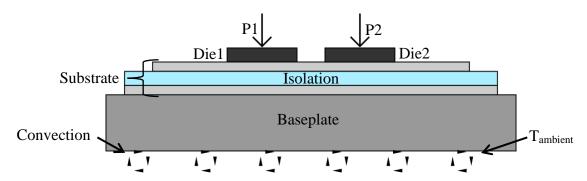

The thermal modeling algorithm is designed around the general structure of an MCPM which can be seen in Fig. 2.1. Some power semiconductor die reside on the top layer of the MCPM. These die produce heat energy, due to ohmic and switching losses, which flows downward through the module where it is released into the ambient environment at the bottom

surface of the baseplate. An effective convection coefficient is used to model the process by which heat flows from the baseplate bottom surface into the ambient environment. The baseplate may in actuality be attached to an air or water cooled heat sink, but the effective convection coefficient allows for modeling of these different cooling systems without complex simulation techniques. The rest of the surfaces of the module are assumed to be perfectly isolated from the surrounding environment such that all heat energy flows by conduction through the solid materials which comprise the module [7], [8].

Fig. 2.1: Cross section of MCPM showing thermal boundary conditions.

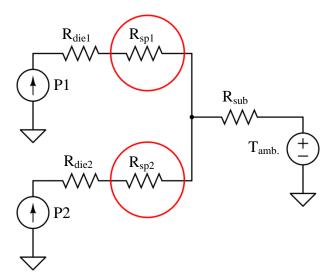

A lumped element heat transfer network topology, shown in Fig. 2.2, is developed based upon the previously described heat flow problem through an MCPM. A lumped element heat transfer network models heat flow in a system analogously to electric currents in an electric circuit. The materials which comprise the different layers of an MCPM each have some finite thermal conductivity which corresponds to the thermal resistances shown in Fig 2.2. As heat energy flows through the thermal resistances in the network, represented by P1 and P2 in Fig. 2.2, temperature differences or voltages by analogy are formed across each thermally resistive layer [7], [8].

The temperature value at each node represents the average temperature across the corresponding surface of that layer. For example, the top surface of Die1 in Fig. 2.1 is represented by the node which connects the heat source or current source in Fig. 2.2 to the left side of thermal resistance,  $R_{\text{die1}}$ . The total thermal resistance of all of the layers from the bottom surface of the baseplate to the top surface of the substrate is formed into a lumped thermal resistance,  $R_{\text{sub}}$  [7], [8].

Fig. 2.2: Lumped element heat transfer network representation of MCPM.

The resistors circled in red in Fig. 2.2 represent a certain type of thermal resistance called thermal spread resistance. This type of resistance does not correspond to a physical layer in the module, but to an effect which occurs when heat flows from a layer with smaller cross-sectional area to larger cross-sectional area. The heat flux in one layer is at a higher density than in the succeeding layer. Thus, there is an interstitial portion of space where the heat flux is spreading out to match the lower density of flux. This spreading of heat flux is approximated by the spread resistances,  $R_{sp1}$  and  $R_{sp2}$ , in Fig. 2.2 [7], [8].

As the layout of a module changes, the bulk of the thermal resistance change occurs in the spread resistances. As long as the overall size and material properties of a module do not change, the change in spread resistance between the bottom surface of the die and the top surface of the trace can be accurately approximated with changes in trace layout and die positioning. The spread resistance is approximated using temperature and heat flux distributions characterized for each die used in an MCPM. If a number of die are identical (the same dimensions and material), the same characterization can be used for the group [7], [8].

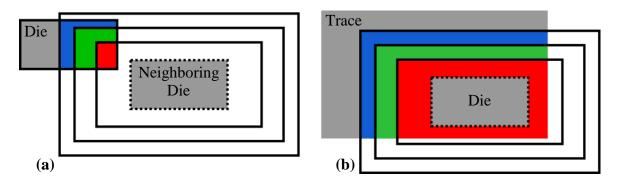

Fig. 2.3: Thermal model rectangular contours. (a): Temperature contours intersecting with neighboring die. (b): Heat flux contours intersecting with trace.

The thermal modeling algorithm breaks the spreading resistance into two major components. The first is a thermal coupling component which is calculated for a given die using

the superposition of neighboring die's temperature distributions onto the die's footprint, shown in Fig. 2.3(a). The temperature distribution of each neighboring die is represented as a set of rectangular contours (Fig. 2.4). The rectangular representation of the distribution allows for fast integration of the neighboring temperature distributions in the region of a die's footprint [7], [8].

The second is an edge effect component which is calculated using the heat flux distribution for a given die, shown in Fig. 2.3(b). Again, the heat flux distribution is represented by a set of rectangular contours. Except this time, the contours are intersected with the trace in which the die is mounted on. As the die approaches closer or farther away from the edge of the trace, more or less of the contours intersect with the trace. When more contours intersect with the trace, more effective cross-sectional area exists for heat energy to flow through thus decreasing the spread resistance [7], [8].

Fig. 2.4: Temperature distribution overlaid with rectangular contour approximation.

The temperature and heat flux distributions used in the thermal model discussed above are acquired through an FEM-based model of an MCPM. Every type of heat producing device

used in an MCPM such as diodes or MOSFETS, needs to undergo a thermal characterization. A separate FEM model is built and solved for each type of device and the temperature and heat flux distributions for each are fitted and saved. Further information about the rectangular contour fitting process is described in [7], [8].

#### 2.3 Automatic Thermal Characterization

## 2.3.1 FEM Tool Background

In order to conduct a finite element analysis (FEA) on a model, a meshing system and FEM solver are needed. The meshing system breaks a geometric model of a system into a finite and discrete set of elements or finite elements. The elements are tied together based on their shared boundaries with each other by equations which approximate a particular partial differential equation (PDE). As a geometric model is further subdivided into smaller elements, a better approximation to a true solution of the PDE is achieved, yet simultaneously this increases computational time and cost. The heat equation is the PDE used for modeling the thermal conduction processes in this particular section [10].

The solver portion of the FEA process takes the meshed elements of the geometric structure and based on the boundary conditions placed on the system and chosen PDE outputs a solution to the problem. At a more detailed level, the elements are tied together by equations and thus form a large system of equations which are represented by a matrix and input vector. The input vector for a heat equation problem would be the heat flux entering the system at the top of a device. An output vector representing some value, such as temperature, at each node in the mesh is found by the solver. The solver may be able to use a number of techniques to solve the large system of equations depending on the type of problem at hand [10].

#### 2.3.2 FEM Tool Selection

ANSYS and SolidWorks are two different tools used to build thermal simulations used for manual characterization. Each of these two tools combines geometric design, meshing, and FEM solving into one software package [11], [12]. Either tool is sufficient for conducting the simulations needed to gather thermal characterization data for modules, but in order to automate the design process some additional aspects are considered such as automation capability, operating system portability, data extraction, simulation accuracy, and software licensing cost.

In order to address some of these issues, open-source alternatives for meshing and solving finite element problems were explored. The open-source meshing tool, Gmsh, allows for automated mesh generation from a geometry description file [13]. The open-source FEM solver Elmer can solve a desired PDE on a mesh generated by Gmsh [14]. Using these two tools in conjunction with each other allows for a complete automated characterization process starting from design geometry input to thermal data output.

Both of these open-source tools, as well as ANSYS, allow for great portability as they are available on Windows and Linux based operating systems. SolidWorks on the other hand is only able to execute in a Windows environment. Both SolidWorks and ANSYS have automation capabilities, so all of the tools considered cover this criterion. Data extraction capability is also covered by all of the above tools. In terms of simulation accuracy, Gmsh and Elmer provide accurate results as compared to SolidWorks for similar thermal problems. A comparison of the two is shown in Section 2.3.4. Since ANSYS and SolidWorks are both commercial tools, a software license needs to be obtained in order to operate them. The open-source license used by Gmsh and Elmer allow for wide distribution of the tools for free. Under these criteria, Gmsh and

Elmer were selected for automation of the thermal characterization process. The following sections detail the meshing and finite element analysis setup used in PowerSynth.

## 2.3.3 Meshing with Gmsh

The Gmsh meshing program outputs a mesh for some input geometry. Gmsh takes a file format with extension ".geo" that contains instructions on how to build a specific geometry in either 2D or 3D space. Once the ".geo" file is loaded and constructed, the geometry can be meshed.

Geometry in a ".geo" file is described by a special scripting language interpreted by Gmsh, and is built up from a set of points, lines, surfaces, and volumes. Each point, line, surface, etc. is created as a programming object in the scripting language and can be manipulated as such. The first primitive components used to describe the model's geometry are collections of points which can be used to form lines. Next, collections of lines are used to form surfaces and collections of surfaces to form volumes.

A rendering of a loaded geometry file is shown in Fig. 2.5(a). The module structure for the thermal characterization is a stack of rectangular volumes (boxes) in contact with each other. Since the ".geo" file is a script, it is written to take a list of box dimensions as input each with a width, length, and thickness. Each box is assumed to be centered at the origin. The first three box dimensions in the list represent the lowest box on the z-axis (the baseplate), and the last dimensions represent the highest box (the die under characterization). The script takes the list of box dimensions and generates the points, lines, surfaces, and volumes associated with each box at the proper locations in space. The ".geo" file or script can be found in Appendix A.

Fig. 2.5: Module characterization setup with die in center. (a): Surface rendering of module. (b): Module model with meshing.

After the model geometry is constructed in Gmsh by loading the ".geo" file, the model is meshed. The granularity of the mesh is selected by applying a characteristic length to each point in the model, e.g. the box layer corners. Gmsh will attempt to match the edge lengths of the tetrahedron finite elements to the characteristic length of each point and linearly interpolate the lengths between points accordingly. The frontal meshing algorithm is selected in Gmsh as the meshing algorithm which produces tetrahedral elements. Gmsh ensures nodes on surface boundaries match and that the entire model forms a coherent solid mesh [13]. The surfaces of these tetrahedral elements can be seen in Fig. 2.5(b) and Fig. 2.6.

Fig. 2.6: Close-up of meshed die and die attach layers.

The characteristic length used in the meshing of relatively thin layers needs to be considered. The solder or die attach layers are usually thin with respect to the surrounding die and metal layers. If the length chosen is too small, the meshing algorithm may take long amounts of time in order to create a fine enough mesh for the thin layer or may even fail. If the length is too large the meshing algorithm may generate incorrect or badly sized elements for the thin layer. Using the same characteristic length as the die mesh is found to work in many situations. This may be due to easing the node matching between the die and solder layer. The interaction between these two layers can be seen in Fig. 2.6.

The entire process described above can be executed via command line by Gmsh, thus no graphical user interface interaction needs to take place. Gmsh is called with arguments which point it to the correct ".geo" file and mesh algorithm selected. Gmsh reports back as to whether the meshing process was successful or not.

### 2.3.4 Finite Element Analysis with Elmer

After the mesh generation process, the FEA problem needs to be set up and solved. This is achieved by writing a ".sif" file which is passed to Elmer, the FEM solver. The materials of the model need to be described in terms of density and heat conductivity in order to solve the heat equation. The boundary conditions of the model also need to be setup.

The different material properties of each layer in the model are applied and identified by volume numbers given to each layer in the original ".geo" file used by Gmsh. Gmsh retains these identification numbers in the output mesh file. Collections of points, lines, or surfaces can also be identified in the same way. Each layer is given a unique volume number such that the correct

material properties can be properly attributed to each layer in the ".sif" file. An example ".sif" file is shown in Appendix B.

The boundary conditions are assigned using a similar method, except surface identification numbers are used instead. The top surface of the die is given a numeric identifier, and a heat flux value is assigned to the surface corresponding to the total heat flow power dissipated from the die for characterization. The next boundary condition, a convection process, is applied to the bottom of the baseplate through the same method. All of the other outer surfaces default to a perfectly isolated state.

After the problem has been defined, the system needs to be solved. The solutions to a finite element system are never perfect. There is some tolerance of error allowable in the solutions, similar to a SPICE solver. If the convergence tolerance is set too large, the amount of error in the solution set may be too large. If the convergence tolerance is set too low, the solver may never converge to a low enough error measure. A convergence tolerance of  $10^{-7}$  is found to allow the Elmer solver to converge on a solution quickly and also maintain a reliable amount of fidelity in the solution data (the temperature at each mesh point).

Fig. 2.7: Steady State Thermal Simulation Results. (a): Result from SolidWorks. (b): Result from Elmer.

A comparison between a model built, meshed, and solved in SolidWorks and Elmer can be seen in Fig. 2.7. The overall temperature distributions in both models are quite similar. Table 2.1 summarizes the minimum, maximum, and average temperature of the two different model solutions. The Elmer minimum temperature result has 0% error with 5 significant digits of precision, and the maximum and average temperatures each have less than 0.1% error, as compared to SolidWorks results. Therefore, Elmer is able to provide high enough quality thermal solutions in order for use in the thermal characterization process.

Table 2.1: SolidWorks vs. Elmer FEA results.

|            | Min. Temp. (K) | Max. Temp. (K) | Avg. Temp. (K) |

|------------|----------------|----------------|----------------|

| SolidWorks | 316.59         | 319.33         | 316.8          |

| Elmer      | 316.59         | 319.28         | 316.7          |

Elmer outputs the solution data in an ASCII text file. The file contains a list of the (x,y,z) coordinates of every node in the problem mesh and a unique integer ID for each node. Each line of node data in the file is delimited by a newline character. A list of temperatures at every node is listed below the coordinates and node IDs in the same order. A separate list of heat flux components flowing in the x, y, and z directions is also contained in the file in a similar manner to the temperatures. The file is parsed for nodes which reside at the same z level as the top of the isolation layer. Once the correct nodes are determined, the temperature and heat flux data is extracted for each distribution. Next, this data set is passed through the fitting portion of the characterization process detailed in previous work [7], [8]. This allows the entire characterization process to be completed without human interaction.

## **Chapter 3** Electrical Parasitic Modeling and Extraction Algorithm

#### 3.1 Introduction

The previous work conducted on electrical parasitic modeling, described in Gong's thesis, primarily focuses on the development of physical models that gauge parasitic resistance, inductance, and capacitance rather than the extraction algorithm. The goal of the parasitic extraction algorithm is to produce a circuit representation of a power module in which electrical parasitics are included. This is achieved by breaking a layout design into basic enough elements such that the physical models can be used to evaluate the individual elements' electrical parasitic properties. Once each element's parasitic values are known, they are written into a lumped element circuit representation of the module. Some initial work in parasitic extraction is covered in Gong's thesis, but only a specific case is considered. This work served as a basis for further development of the extraction algorithm. This chapter will reiterate some of the previous work on the physical models and their parameters and describe further developments in the parasitic extraction algorithm [8].

### 3.2 Parasitic Resistance and Inductance Modeling

A micro-strip transmission line structure is used to model the parasitic resistance and inductance in the traces of MCPMs. Fig. 3.1 illustrates the similarities in structure between the two systems. The micro-strip structure consists of an infinite ground plane, a dielectric layer, and a top metal layer. The MCPM structure consists of a finite ground plane (baseplate), a dielectric layer (isolation), and a top metal layer (trace). The primary difference between these two structures is the finite versus infinite ground plane. The infinite ground plane approximation of

the micro-strip line structure models the parasitic resistance within 10% accuracy of a FEM model of the system, but does not model the parasitic inductance with as much accuracy. The ground plane has a much more dominant effect on the inductance of the traces in the system, thus having a finite dimensioned ground plane affects the quality of the inductance model. In order to improve accuracy, an average between the inductance of an isolated bar and the micro-strip line is taken. This averaged model improves the error for the inductance to around 10% for individual trace lines [8].

Fig. 3.1: Comparison of micro-strip transmission line structure and MCPM structure [8].

The main benefit to modeling the inductance and resistance of the traces with a microstrip transmission line model is that a closed-form equation is used to find the values based on simple geometric and material parameters. If an MCPM layout is broken into strips of rectangular trace, the micro-strip equations can be easily applied to this system and at very low computational cost to estimate the parasitics of the total layout. In terms of computational cost, the algorithm was found to run around 1 million times faster than a full FEM analysis.

Another contribution to parasitic inductance and resistance in a layout comes from the bondwires which connect from device to trace or trace to trace. Closed-form equations which

include frequency dependent effects such as the skin-effect were researched and found to model the inductance and resistance of bondwires effectively. Although further research is required in order to consider the effects of mutual inductance between the wires. Documentation regarding the verification and equations of the previously described models can be found in [8].

## 3.3 Parasitic Capacitance Modeling

A similar closed-form equation based approach is used for modeling the parasitic capacitance of the traces in MCPMs. The primary capacitance for each trace exists between the second metal layer and the top metal layer of an MCPM, as seen in Fig. 3.2. The coupling capacitance spanning from trace to trace is typically several orders of magnitude smaller than the aforementioned substrate capacitance, thus is not included in the modeling effort. Coupling capacitance between traces is generally quite small due to the small vertical sides of the trace with respect to the distances in which trace is separated. Coupling capacitance plays a larger role in integrated circuit layouts because the interconnect aspect ratio is closer to 1.0 and horizontal distance between interconnect is relatively closer. Mutual inductance between traces plays a far greater role in unwanted coupling inside a power module. Research effort spent on modeling mutual inductive coupling would be far more effective in exploring coupling issues [8].

Fig. 3.2: Parallel plate and fringing field lines which make up parasitic capacitance [8].

The substrate capacitance, measured from the trace layer to second metal layer as shown in Fig. 3.2, is estimated by summing together the capacitance from the parallel plate capacitance equation and a fringe capacitance equation. The fringe capacitance equation approximates the amount of capacitance due to field lines extending from the sides of a piece of trace to the substrate. The model increases in error as the distance between the trace and substrate is increased, due to the complex effects of the fringing field lines around the perimeter of the trace. The fringing field lines pass through both the passivation coating and the isolation dielectric material which affects the fringe capacitance value. Since the passivation coating is typically quite thin as compared to the thickness of the isolation layer, the permittivity for the passivation material is left at a value of air or vacuum. The summed model of simple parallel plate capacitance and fringe capacitance yields less than 7% error for typical power module parameters and reaches a maximum of 26% error as isolation thickness, h, is increased to a maximum of 0.8 mm in the verification study presented in [8]. A typical isolation thickness for a high-voltage (1200 V) MCPM substrate is around 0.64 mm or less. This is well within bounds for accurate substrate capacitance estimation.

### 3.4 Parasitic Extraction Algorithm

A graph is used as the primary data structure to hold the extracted parasitic information. A graph is composed of two basic elements known as nodes or vertices and edges. The circuit schematics electrical engineers use every day are also simple graphs with nodes and edges. In circuit schematics, the nodes are known as nodes and the edges as branches. Passive circuit elements such as resistors, capacitors, and inductors span two nodes and thus constitute a branch. An example parasitic graph is shown in Fig. 3.3, where each edge holds inductance, resistance,

and substrate capacitance values between layout nodes. This graph is not a circuit schematic, although it bears a close resemblance. The nodes in Fig. 3.3 represent either connection points between traces labeled in green, lead connections labeled in blue, or device connections labeled in red. A circuit schematic in the form of a SPICE net-list can be constructed from this parasitic graph, and the process is detailed in Tucker's Honor's thesis [15].

The graph data structure is implemented using a Python graph library called NetworkX [16], [17]. A NetworkX graph is constructed by adding nodes and edges to a graph programming object. Multiple attributes can be attached to any node or edge in the graph. An attribute consists of a key-value pair. The key is usually a string which gives the name of an attribute, and the value carries the value of the attribute. For example, the edges in the parasitic graph each have at least three attributes with key names "res", "ind", and "cap" representing resistance, inductance, and capacitance, respectively. The particular values for each key are floating point numbers representing the amount of resistance, inductance, or capacitance in the edge element. The value of attributes associated with nodes and edges need not be simply numbers. The nodes which connect to devices or leads have attributes whose values reference a programming object which holds various parameters and methods for that device or lead.

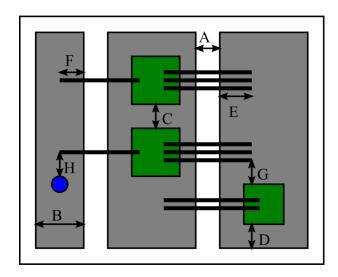

Fig. 3.3: Graph based representation of parasitic network.

The layout of the power modules in this thesis are described by a set of rectangular traces. The individual trace rectangles can be seen in green in Fig. 3.4, where each is surrounded by a light black border line. The parasitic graph is created based on this set of rectangles. Each trace rectangle is oriented in either a horizontal or vertical way except for a special case of trace rectangle called a super-trace. A super-trace has neither vertical nor horizontal orientation in particular and is dealt with on both axes. The terms horizontal and vertical in this context refer to the x-axis and y-axis, respectively, and not vertical in the z-axis sense.

Since each trace rectangle has some orientation associated with it, a set of points can be formed along the length of each trace rectangle. This set of points or nodes, called spine nodes, run along the length of a trace and reside in the middle of the width of a trace. The spine nodes are placed based on whether there is a connected trace, device, lead, or bondwire along the

length of the trace. The spine nodes for a vertical trace rectangle are pointed out in Fig. 3.4. The first point from the top is a trace connection node and the next three are device connection nodes.

Fig. 3.4: Module layout with overlaid parasitic graph.

The spine nodes are allocated by iterating through each trace rectangle object and identifying if there are leads, devices, bondwire connections, or trace connections made at certain points along the length of the trace. This information is bound to the trace rectangle object through another data structure in the system called a symbolic layout. Symbolic layouts are described in more detail in a forthcoming chapter, but basically contain information about the connectivity of traces and what leads and devices reside on traces in a symbolic form rather than a purely geometric form.

Once the spine nodes are added for a given trace, they are sorted in geometric order from lowest to highest. For example, if a trace is oriented vertically, the spine nodes will vary from some lower y coordinate to some higher y coordinate. After the spine nodes have been sorted, they are iterated over from lowest to highest coordinate and connected together with graph edges ensuring the nodes are connected together in correct geometric progression. Each spine node is

associated with one other node, either connecting to a device, lead, bondwire, or trace connection. Edges connecting these "off spine" nodes are also created, forming interconnections between traces and other objects in the network. Sometimes the connected object resides directly on the spine of the trace, such as the devices positioned in the middle of the traces in Fig. 3.4, thus an "off spine" connection node and edge is not needed.

The super-trace nodes are allocated differently. The geometric representation of a super-trace is still a rectangle. The super-trace rectangle is able to span multiple normal trace rectangles. There exist two super-trace rectangles in Fig. 3.4, in which they span two normal vertical trace rectangles above them. The super-trace rectangle on the right in Fig. 3.4 spans two horizontal trace rectangles also. Since a super-trace is able to span multiple horizontal and vertical trace rectangles, this means multiple connections can be made to the trace on both axes. Instead of a single spine of nodes, a mesh of nodes and edges is needed to facilitate the multiple connections which can be made on both axes.

The mesh is generated by considering the horizontal and vertical axes separately and finding trace connections made on either axis. Next, a matrix type mesh is created based on the number of trace connections made on the vertical and horizontal axes. On each axis, initially two points are added regardless of any trace connections on them. Next, a point is added for each trace connection on each axis. The total number of nodes in the matrix mesh will be the number of points on each axis multiplied by each other. For example, the right-hand super-trace in Fig. 3.4 has two vertical traces connected to the top of it and one horizontal trace connected to the left-hand side of it. This yields 4 points on the horizontal axis and 3 points on the vertical axis.

Thus, a total of 12 nodes are seen in the body of the mesh of the super-trace. The resulting mesh is a non-uniform grid.

As the nodes for each trace rectangle are being created and connected together with edges, the parasitic models are also evaluated based on the particular dimensions of each trace and the distance between two nodes on the spine of each trace. Each of these pieces is referred to as a trace segment. These trace segments are rectangular in shape which allow the micro-strip transmission line equations and parallel plate capacitance equations to be easily evaluated for each. Fig. 3.5 illustrates trace segmentations in one half of a layout on the right side of the image, and the associated lumped element network of inductances on the left. This figure is to demonstrate that there is some parasitic inductance, resistance, and capacitance associated with each trace segment. The trace segments which run along the spine of a trace take on the width of that trace. In the case of trace segments which do not reside on a trace spine, such as a segment connecting to a lead or bondwire connection, these take on the width of the connected lead or total width of the connected bondwires.

Fig. 3.5: Parasitic extraction lumped element network and trace segmentation.

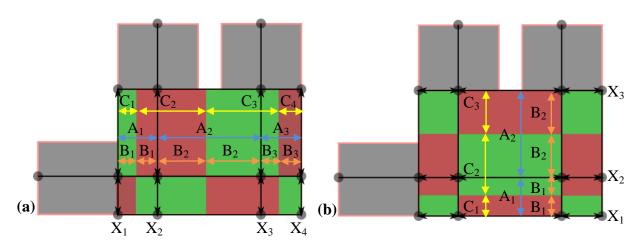

The super-trace edges also need a segment width and length in order to allocate an accurate parasitic value for each edge element. Fig. 3.6 illustrates the segmentation concept for a 4 column and 3 row super-trace meshing. Fig. 3.6(a) and 3.6(b) show the vertical (column) and horizontal (row) segmentation cases, respectively. The red and green rectangles represent the geometric size of each segment and the black lines with double arrowheads represent the corresponding graph edges. The segment length for each edge (vertical or horizontal) is simply the length of the edge itself or the distance between the two nodes which make up the edge.

The width segmentation process is also dealt with in terms of rows and columns which are denoted by  $(X_1, X_2 ... X_N)$  where N is the number of rows or columns (Fig. 3.6). Each graph edge receives some segment width  $(C_1, C_2 ... C_N)$  which is shared with each edge in the row or

column. The graph edges on the super-trace boundaries have widths  $C_1$  and  $C_N$  which take on a width equal to half the horizontal or vertical distance to their nearest neighboring edge represented by  $B_1$  or  $B_{N-1}$ . The symbols  $A_n$  in Fig. 3.6 represent the distance between column or row  $X_n$  and  $X_{n+1}$ , and  $B_n$  represents half this distance. The internal columns or rows  $(X_2 \ldots X_{N-1})$  take on a width of  $B_{n-1}+B_n$  where n is the current column or row. This width segmentation process ensures that the total width of the segments  $(C_1 \ldots C_N)$  is equal to the width of the super-trace in the vertical and horizontal directions.

Fig. 3.6: Super-trace segmentation with segment widths marked with yellow lines. (a): Vertical segments. (b): Horizontal segments.

The micro-strip transmission line equations used for calculating the inductance of each segment in the extracted layout only yield accurate results for segments whose aspect ratios are less than 1.0 [8]. The aspect ratio, defined as width divided by length, of segments in layouts is frequently greater than 1.0. In order to help approximate the inductance of segments more effectively, the maximum aspect ratio of segments is constrained to 1.0 by automatically reducing the segment width to be equal to the segment length in these cases. The inspiration behind this solution is that the current in wide traces is not usually uniformly distributed

throughout the trace anyway. A reduction in the effective width of the trace generally helps improve the inductance estimation for most layouts.

## 3.5 Parasitic Network Measurement

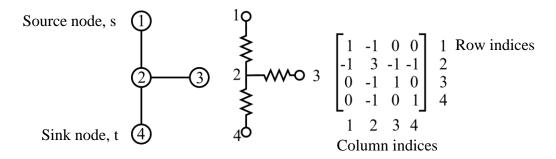

It is useful to be able to measure the effective resistance or inductance between two different nodes in the extracted parasitic network, such as measuring the loop inductance in an H-bridge or the gate loop inductance between the gate and source leads of switching positions. The extracted parasitic network takes the form of a graph and can be converted into a Laplacian matrix from this graph data structure. The Laplacian matrix of a graph is similar to the admittance matrix of a circuit used in SPICE simulators [18], [19]. The construction of a Laplacian matrix allows fast measurements of resistance or inductance between nodes. Fig. 3.7 shows a simple parasitic graph with each node given a unique integer and its corresponding Laplacian matrix to the right. The node integers index the rows and columns of the Laplacian matrix.

Fig. 3.7: Graph and Laplacian matrix with all edges weighted to 1.0 (1.0  $\Omega$ ).

The Laplacian matrix is constructed either by an element stamping method, nodal analysis, or some other means [18]. Fortunately, there exists a function in the NetworkX graph library which can produce a Laplacian matrix from a graph. Although, a weight value for each

edge in the graph needs to be specified. If the goal is to measure resistance between two nodes in the graph, the desired weight value on each edge would be the conductance or inverse of resistance. If measuring inductance, each edge weight will take on the inverse of the inductance value stored in each edge element. The key-value attribute system described earlier allows the specification of these weighting values for the NetworkX Laplacian matrix function. As long as a key-value pair for conductance and inverse inductance exists for each edge in the graph, a corresponding Laplacian matrix for the system can be constructed for each type.

The effective resistance is measured between two nodes by applying a unitary flow between the two nodes. If a unitary current is made to flow between the two nodes, a potential difference equal to the effective resistance will appear across the nodes via Ohm's law: V=R if I=I. The effective inductance can also be found in this way, because inductive elements follow the same mathematical rules as resistive elements when placed in series or parallel configurations. The unitary current applied between the nodes in the inductive case is not a real current, but simply a mathematical tool to aid in finding the effective inductance between the two nodes.

The effective resistance can be found using the Laplacian matrix derived from a parasitic graph via the following linear algebraic equation:

$$R_{eff}^{s,t} = \mathbf{x}_{s,t}^T \mathbf{L}(\mathbf{G})^{\dagger} \mathbf{x}_{s,t} \tag{3.1}$$

where  $x_{s,t}$  is a vector of net electrical flows between a source node s and sink node t, and L(G) is the Laplacian matrix of the parasitic graph G. The vector of electrical flows  $x_{s,t}$  is a vector which has the same number of entries as there are nodes in G and carries the same node indices.  $x_{s,t}$  has a 1 in the node index position which represents the source node and a -1 in the position

which represents the sink node. Thus, the net current in the system is conserved. All other entries in  $x_{s,t}$  are zero which means no other net currents are flowing between any other nodes in the system. In a SPICE admittance matrix, the row and column entries associated with the ground node are removed e.g. the 4<sup>th</sup> index in Fig. 3.7. If not removed, a net negative current would be seen flowing in the ground node position of the  $x_{s,t}$  flow vector. These rows and columns are not eliminated in this mathematical procedure, because this allows for Eq. (3.1) to be used for effective resistance calculations [19].